# Swan-2<sup>™</sup> ES4318 DVD Processor Chip Data Sheet

#### **OVERVIEW**

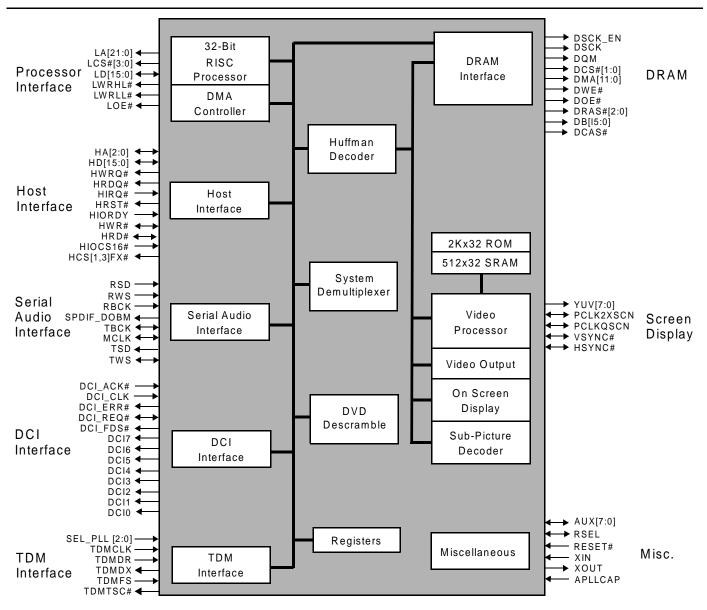

The Swan-2<sup>™</sup> ES4318 Processor is a single-chip solution for a Digital Versatile Disc (DVD) player that integrates MPEG video decoding, DVD system navigation, Content Scrambling System (CSS), and Dolby<sup>™</sup> Digital (AC-3) and MPEG audio decoding. The fully programmable Swan-2<sup>™</sup> ES4318 is based on a proprietary ESS architecture. It offers the best feature set in comparison to any currently existing DVD chip, and a glueless interface to various peripheral components. The Swan-2<sup>™</sup> ES4318 is the most cost effective solution in its class with an integration level and quality that set new benchmarks.

The Swan-2™ ES4318 processor is capable of decoding Dolby™ Digital (AC-3) or DTS digital surround, simultaneously with MPEG-1 or MPEG-2 video. For embedded applications, the Swan-2™ ES4318's internal RISC processor can be used in place of a microcontroller to provide all system control, DVD system navigation, CSS decryption, and many other features. On-chip, multi-tap filters provide arbitrary scaling with state of the art SmartScale™ technology useful for video standards conversion. SmartStream™ technology from ESS provides video error concealment and video post-processing, leading to the highest playability and video quality. Other features included in the Swan-2™ ES4318 are video letterbox display, DVD Sub-Picture overlay, and On-Screen Display.

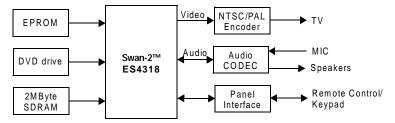

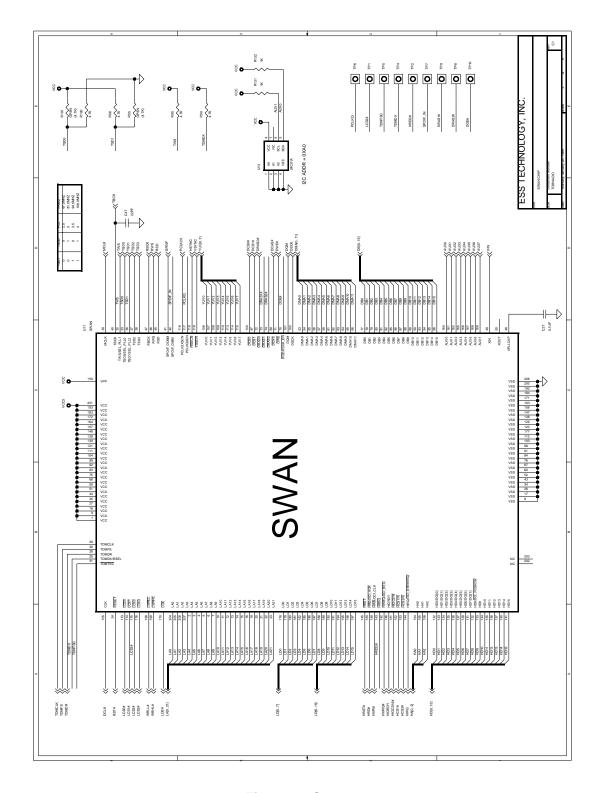

The ES4318 provides a glueless 8/16-bit parallel interface to most DVD servo/loaders. It connects directly with 8/16-bit ROM and 16-bit SDRAM/EDO. An 8-bit YUV video interface supports many TV encoders. General purpose auxiliary pins are provided to control various peripheral devices. A standard I²S interface supports popular audio DACs and ADCs. The ES4318 also features a direct S/PDIF output. Figure 1 shows a block diagram of a typical stand-alone system using the Swan-2™ ES4318 with the glueless SDRAM interface.

The DVD system stream from a DVD disc is passed to the Swan-2<sup>TM</sup> ES4318 through the 8-bit/16-bit parallel host interface. The Swan-2<sup>TM</sup> ES4318 parses the system layer and demultiplexes the audio and video streams. Audio is decoded and passed through the I²S audio serial bus to an external audio DAC and then to the speakers. Video is decoded and output as YUV pixels to an NTSC or PAL video encoder. System control and housekeeping functions (keypad and remote control) are also provided on-chip.

#### **FEATURES**

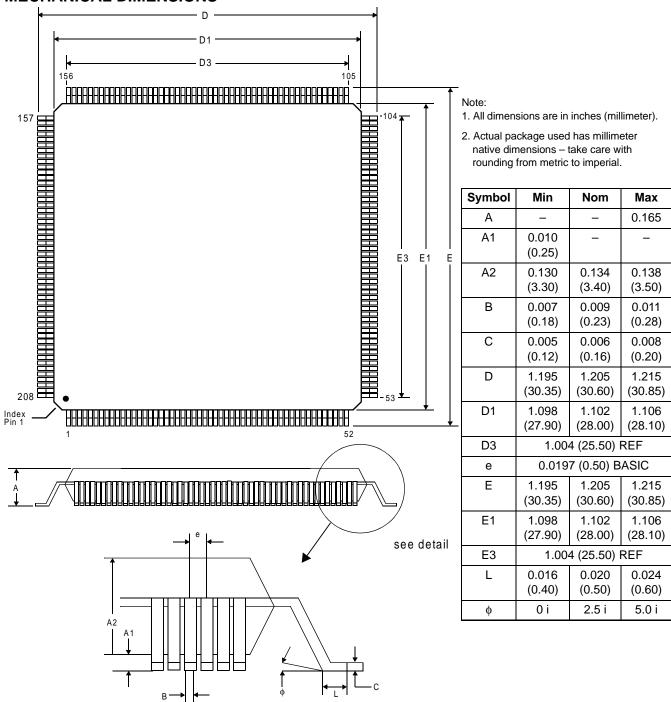

- Single-Chip DVD video decoder in a 208-pin PQFP package

- Supports MPEG-1 system and MPEG-2 program streams

- · Programmable multimedia processor architecture

- Compatible with Audio CD, VideoCD, VCD 3.0, and Super VideoCD (SVCD)

- DVD Navigation 1

- Built-in Content Scrambling System (CSS)

#### Video

- Pan & Scan and Letter-Box conversions

- Trick modes include Slow, Fast Forward, Fast Reverse, Step, and Goto

- Sub-Picture decoder

- 4-bit On-Screen Display (OSD) with 4-bit blending

- 8-bit YUV component video output

#### Audio

- Built-in Karaoke key-shift function

- Dolby<sup>™</sup> Digital 2-channel downmix audio output for Dolby<sup>™</sup>

- Dolby Pro Logic

- · Linear PCM streams for 24 bit/96KHz

- Concurrent S/PDIF out and 2-channel audio output

- Sensaura Dolby Digital Virtual Suround

- DTS Digital Surround 2-channel downmix stereo output

- S/PDIF output for encoded AC-3, DTS Digital output or Linear PCM

#### **Peripheral**

- Glueless interface to DVD loaders (ATAPI or A/V bus I/F)

- Bidirectional I<sup>2</sup>S audio interface

- Direct servo/loader interface

- 8 general-purpose auxiliary ports

- Single 27 MHz clock input

# Smart Technology

- SmartZoom<sup>™</sup> for motion zoom & pan

- SmartScale<sup>™</sup> for NTSC to PAL conversion and vice versa

- SmartStream<sup>™</sup> for video error concealment

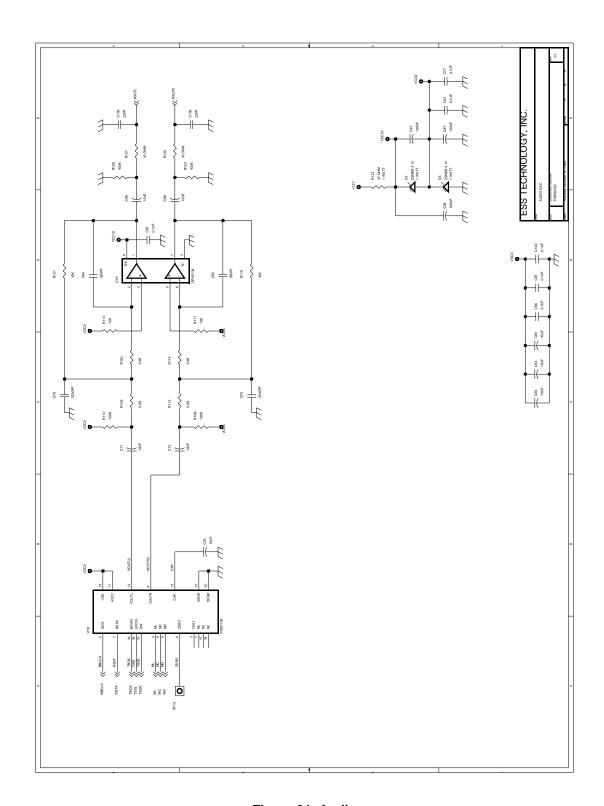

Figure 1 Typical Swan-2™ ES4318 System Block Diagram.

# **CONTENTS**

| OVERVIEW 1                                             | HOST INTERFACE                                                    |

|--------------------------------------------------------|-------------------------------------------------------------------|

| FEATURES                                               | Debug Port26                                                      |

| CONTENTS 2                                             | Command Port26                                                    |

| FIGURES                                                | DMA Port                                                          |

| SWAN-2™ ES4318 PINOUT DIAGRAM4                         | DCI INTERFACE                                                     |

| PIN GEOGRAPHY 5                                        | AUDIO INTERFACE                                                   |

| SWAN-2™ ES4318 PIN DESCRIPTION                         | DCI Timing28                                                      |

| SWAN-2™ ES4318 FUNCTIONAL DESCRIPTION                  | Audio Transmit and Receive Timing Diagrams                        |

| RISC Processor                                         | REGISTERS                                                         |

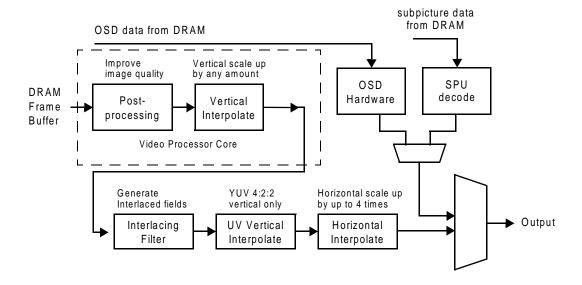

| Video Processor                                        | TDM Registers                                                     |

| Video Output                                           | Host Interface (RISC side) Registers                              |

| •                                                      |                                                                   |

| Huffman Decoder                                        | Host Interface (host side) Registers                              |

| Audio Interface                                        | DCI Interface                                                     |

| DRAM Interface                                         | Audio Registers                                                   |

| On-Screen Display (OSD)                                | Audio Interface Registers40                                       |

| DRAM DMA Controller                                    | S/PDIF Interface Registers                                        |

| TDM Interface 8                                        | Sub-Picture Unit (SPU) Related Registers                          |

| Host Interface                                         | Color Index Registers                                             |

| DCI Interface9                                         | Video Interface Registers                                         |

| DVD Descrambling9                                      | Video (Output) Registers48                                        |

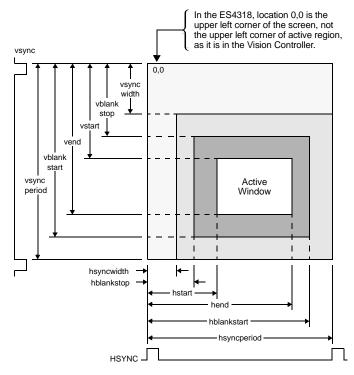

| VIDEO INTERFACE                                        | Bus Control & DRAM Registers54                                    |

| Video Bus                                              | RISC Interface Registers55                                        |

| CRT Controller                                         | (SRAM Interface)                                                  |

| Video Post-Processing                                  | ELECTRICAL SPECIFICATIONS                                         |

| Video Timing                                           | Absolute Maximum Ratings                                          |

| Sub-Picture Unit                                       | Recommended Operating Conditions                                  |

| DRAM INTERFACE                                         | DC Electrical Characteristics                                     |

|                                                        | AC Electrical Characteristics                                     |

| DRAM Configuration Requirements                        |                                                                   |

| DRAM Configuration                                     | Clock Timings                                                     |

| SDRAM Address Mapping                                  | MECHANICAL DIMENSIONS                                             |

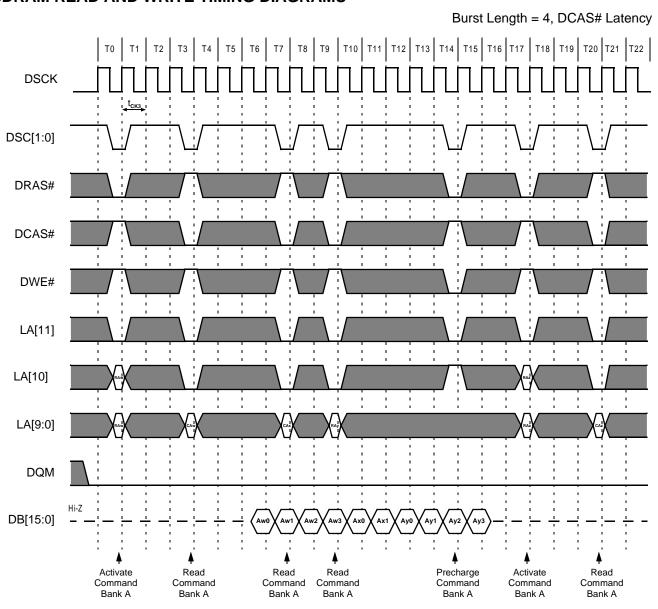

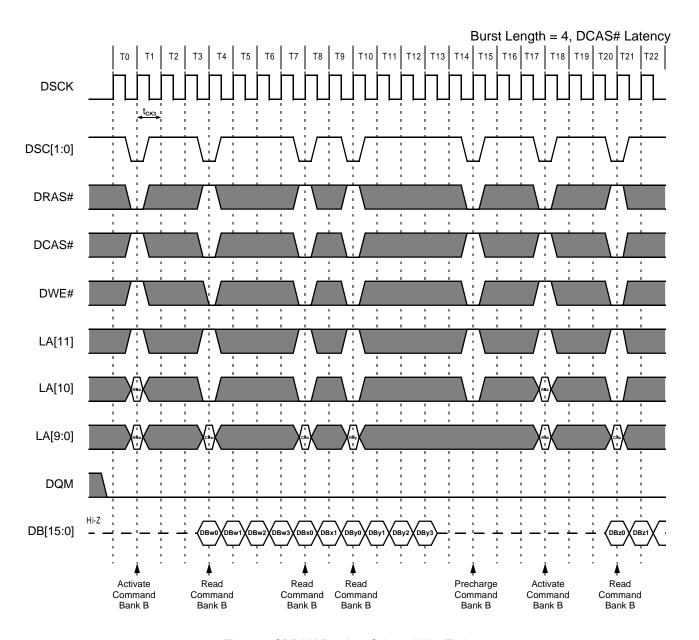

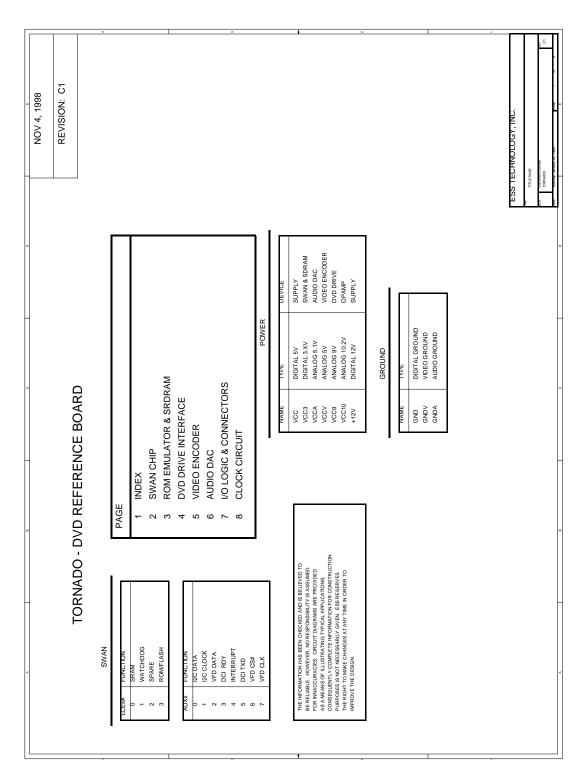

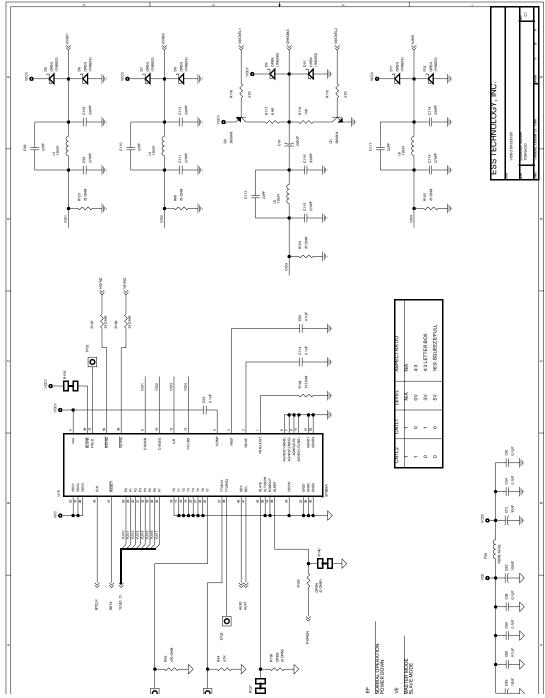

| SDRAM READ AND WRITE TIMING DIAGRAMS15                 | SAMPLE SCHEMATICS62                                               |

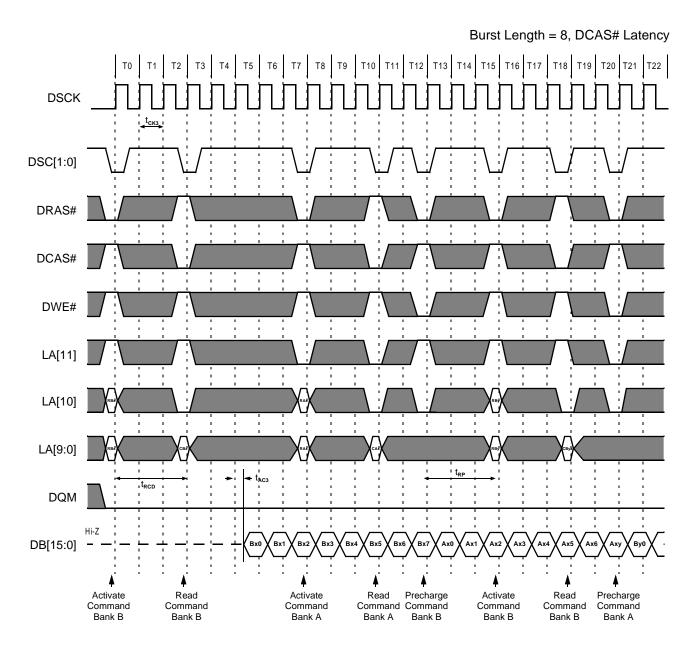

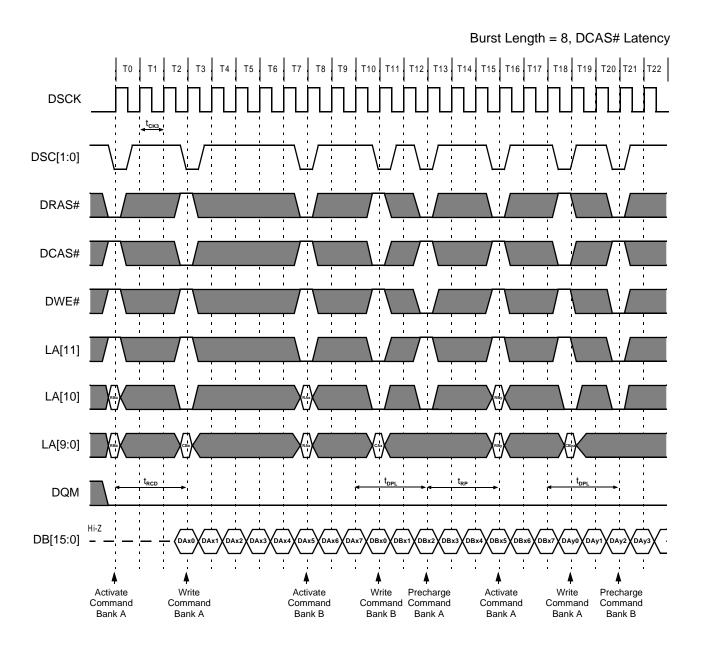

| EDO DRAM READ AND WRITE TIMING DIAGRAMS 21             | APPLICATION NOTES70                                               |

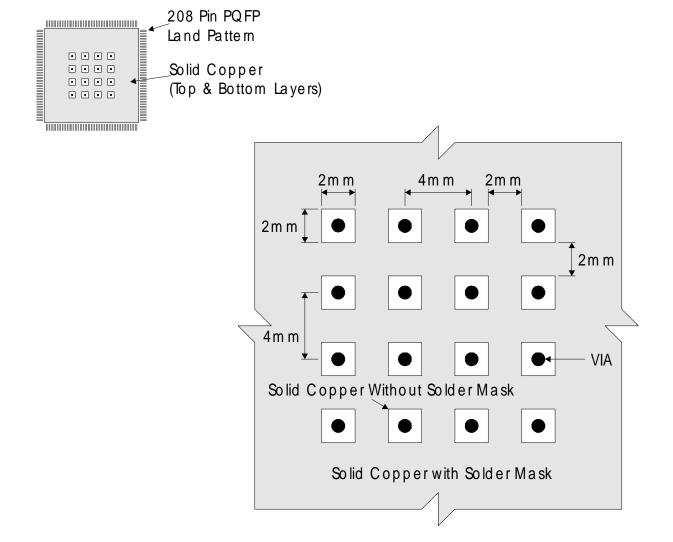

| SRAM INTERFACE                                         | PCB Layout Consideration Regarding Heat Dissipation 70            |

| TDM INTERFACE                                          | Pin 159: Peripheral Protection Voltage                            |

| FIGURES                                                |                                                                   |

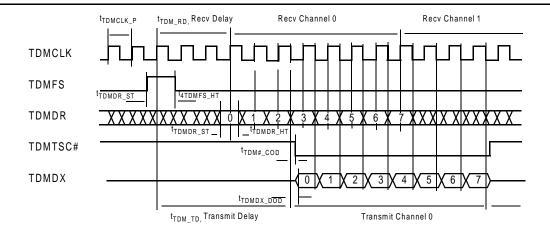

| Figure 1 Typical Swan-2™ ES4318 System Block Diagram 1 | Figure 16 TDM Interface Timing27                                  |

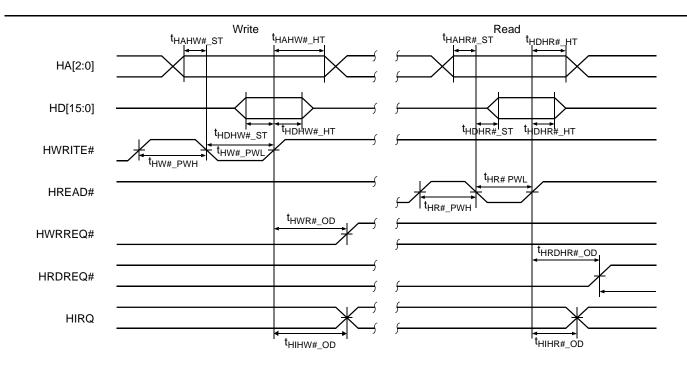

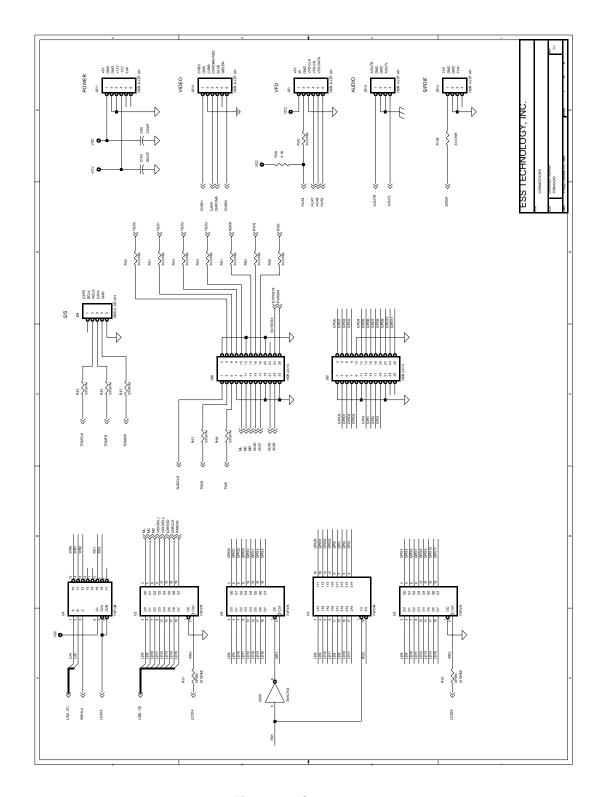

| Figure 2 Swan-2™ ES4318 Pinout                         | Figure 17 Host Bus Timing29                                       |

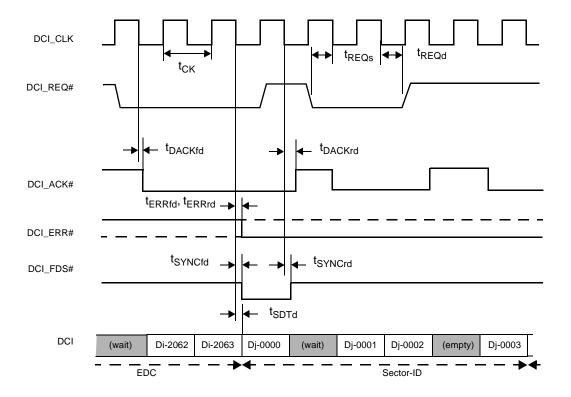

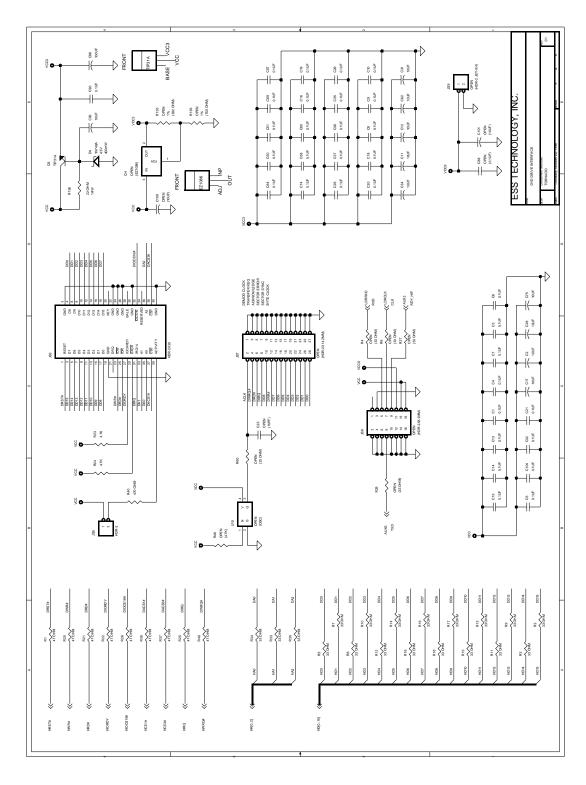

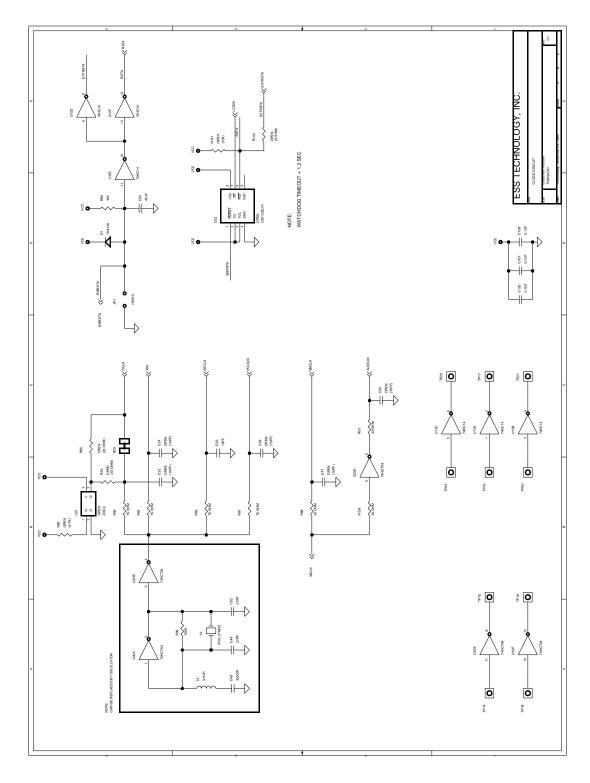

| Figure 3 Swan-2™ ES4318 Block Diagram 9                | Figure 18 DCI Interface Timing                                    |

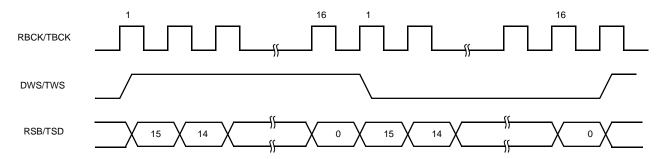

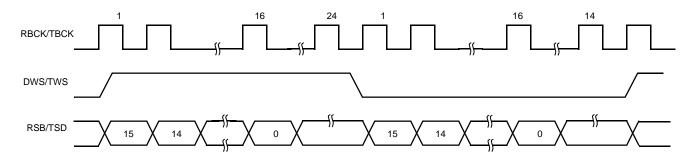

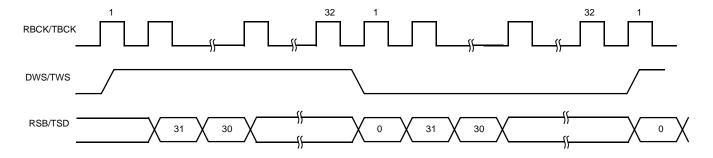

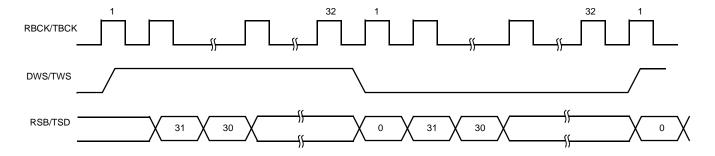

| Figure 4 Video Post-processing                         | Figure 19 Right Justified Mode / 16-Bit Cycle Frame / 16-Bit Data |

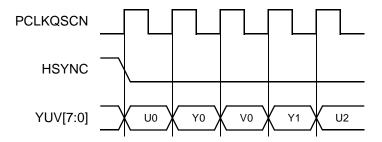

| Figure 5 8-bit YUV Input Timing                        | Frame                                                             |

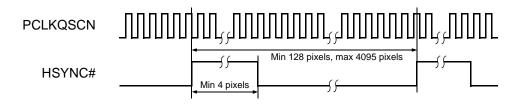

| Figure 6 Horizontal Video Timing                       | Figure 20 Right Justified Mode / 24-Bit Data Frame / First-Bit    |

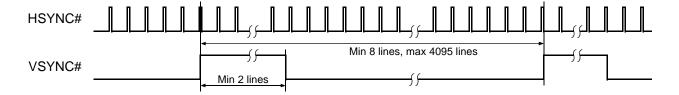

| Figure 7 Vertical Video Timing                         | Sent First / MSB First                                            |

| Figure 8 SDRAM Random Column Read Timing               | Figure 21 Right Justified Mode / 32-Bit Cycle Frame / 24-Bit Data |

|                                                        |                                                                   |

| Figure 9 SDRAM Random Column Write Timing              | Frame / Last Bit Sent Last / LSB First                            |

| Figure 10 SDRAM Random Row Read Timing                 | Figure 22 Left Justified Mode / 32-Bit Cycle Frame / 32-Bit Data  |

| Figure 11 SDRAM Random Row Write Timing 20             | Frame / MSB Firs                                                  |

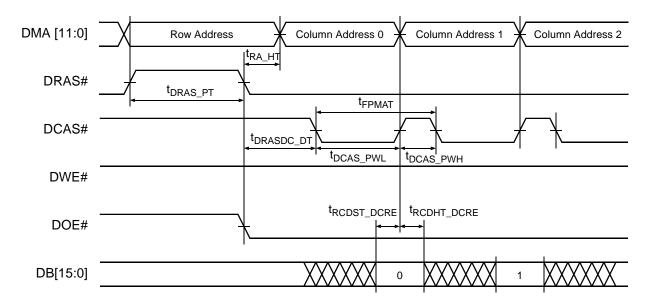

| Figure 12 EDO DRAM Read Timing                         | Figure 23 Video Output Timing                                     |

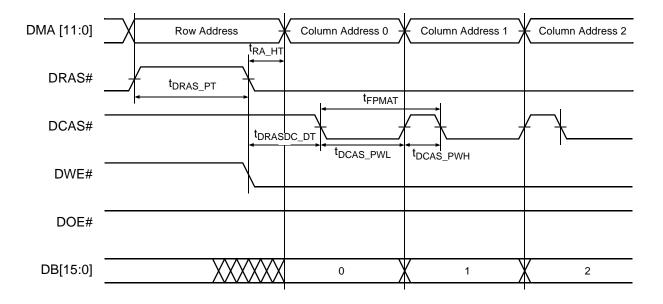

| Figure 13 EDO DRAM Write Timing                        | Figure 24 Swan-2™ ES4318 Clock Timing Diagram 60                  |

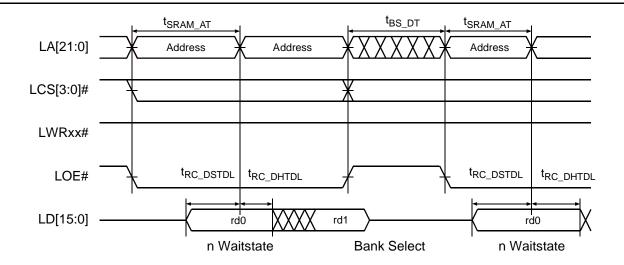

| Figure 14 SRAM Read Timing                             | Figure 25 208-pin Plastic Quad Flat Package (PQFP) 62             |

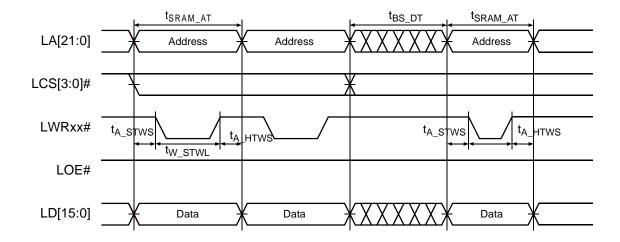

| Figure 15 SRAM Write Timing                            |                                                                   |

| TABLES                                                 |                                                                   |

| Table 1 Various Memory Configuration                   | Table 5 Frequency vs AC Parameter Relationship (-9) 20            |

| Table 2 DRAM Memory Size and Signal Pins               | Table 6 Frequency vs AC Parameter Relationship (-10) 20           |

| Table 3 SDRAM Interface Timing                         | Table 7 DC Electrical Characteristics                             |

| Table 4 Operating AC Characteristics                   | Table / De Electrical enalacteristics                             |

| .a operating to enalacteriotics                        |                                                                   |

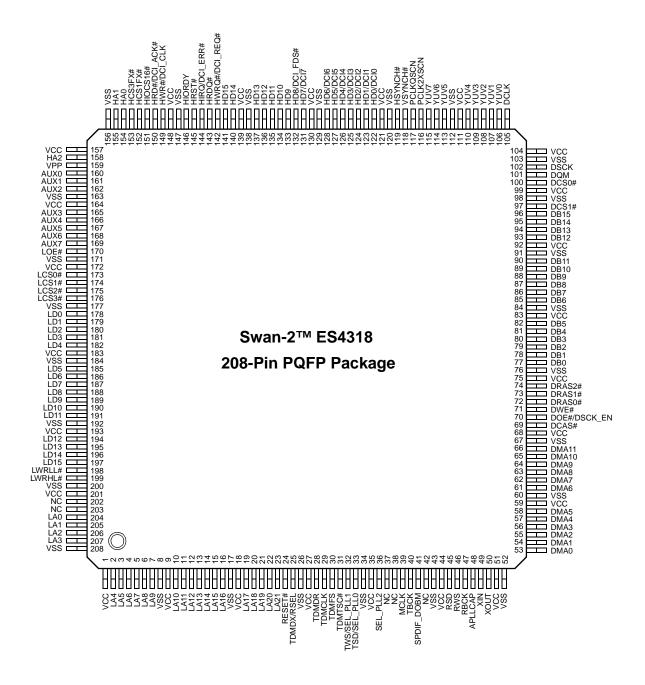

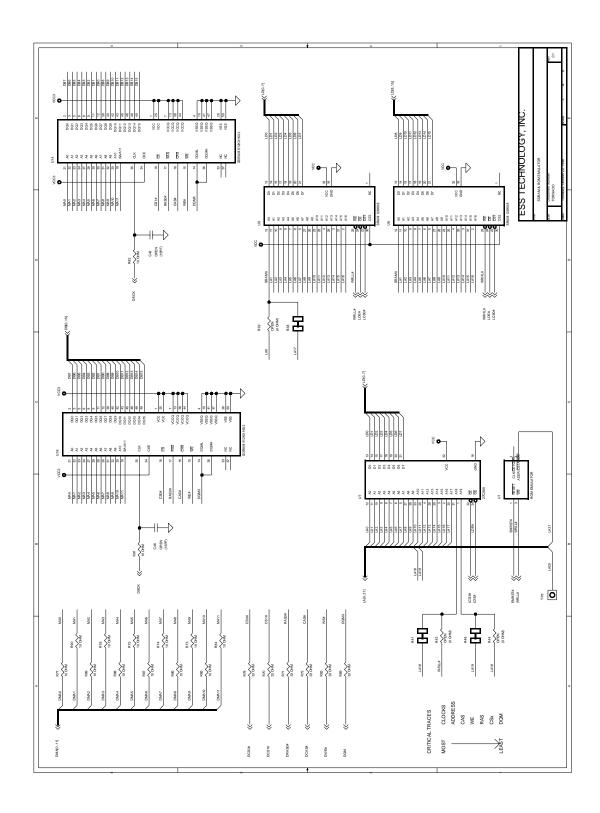

# SWAN-2™ ES4318 PINOUT DIAGRAM

Figure 2 Swan-2™ ES4318 Pinout

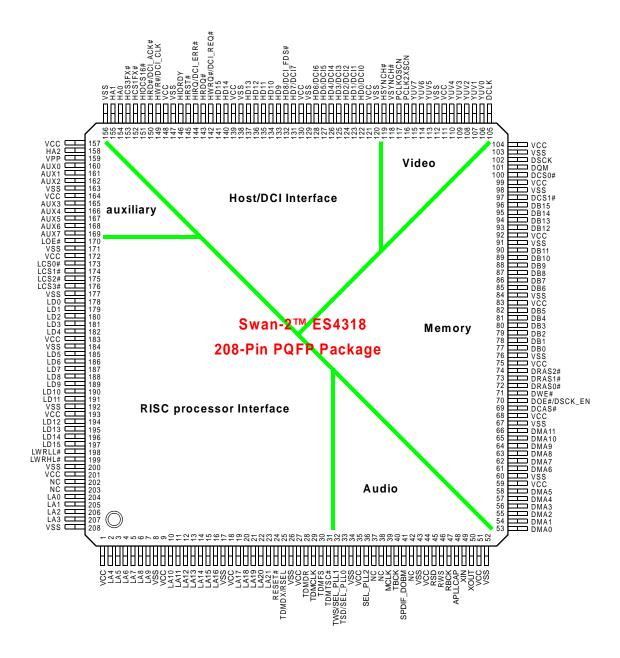

# **PIN GEOGRAPHY**

# SWAN-2™ ES4318 PIN DESCRIPTION

| 1, 10, 10, 11, 12, 12, 13, 13, 14, 15, 16, 16, 17, 18, 18, 17, 11, 14, 17, 12, 19, 13, 10, 14, 17, 18, 18, 17, 17, 18, 19, 20, 20, 20, 20, 20, 20, 20, 20, 20, 20                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Name          | Number                                               | I/O | Definition                                               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------------------|-----|----------------------------------------------------------|

| 121, 101, 101, 101, 101, 101, 101, 101,                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |               |                                                      |     |                                                          |

| LAGYT10    37-518-16-10-7-2-20-7-7-10-10-10-10-10-10-10-10-10-10-10-10-10-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VCC           |                                                      | - 1 | 3.65 V ± 150 mv.                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |               |                                                      |     |                                                          |

| Set   47,159, (93,171,777, )49, (92,002,008                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | LA[21:0]      | 23:19,16:10,7:2,207:204                              | 0   | Device address output.                                   |

| RESET 9  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | VSS           | 8,17,26,34,43,52,60,67,76,84,91,98,103,112,120,129,1 |     | Ground.                                                  |

| RESET 9  1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               | 38,147,156,163,171,177,184,192,200,208               |     |                                                          |

| Tombook                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | RESET#        |                                                      |     | Reset input, active low.                                 |

| RSEL   25                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | TDMDX         |                                                      | 0   | ·                                                        |

| TOMON                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |                                                      |     |                                                          |

| TOMOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | KSEL          |                                                      |     | ROM Select                                               |

| Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |               | 25                                                   |     | RSEL Selection                                           |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               | 20                                                   |     | 0 16-bit ROM                                             |

| TOMAN   TOMA |               |                                                      |     |                                                          |

| TOMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |                                                      |     | 1 8-DIT ROW                                              |

| TOMES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | TOMOR         | 20                                                   |     | TDM receive data                                         |

| TOMPS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |               |                                                      | - ! |                                                          |

| TOMPSIGN   31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |                                                      | ı   | TDM clock input.                                         |

| Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TDMFS         | 30                                                   | - 1 | TDM frame synch.                                         |

| Type                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | TDMTSC#       | 31                                                   | 0   | TDM output enable, active low.                           |

| SEL_PLL1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                                                      | 0   | •                                                        |

| SEL_PLU2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               | 32                                                   |     |                                                          |

| Selec PLLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |               |                                                      |     |                                                          |

| SEL_PLI2   SEL_PLI0   Clock Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |               |                                                      | 0   | Audio transmit serial data port.                         |

| SEL PILIZ   Sele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | SEL_PLL0      |                                                      |     | Select PLL0.                                             |

| SEL PILIZ   Sele                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |                                                      |     | SEL BLID SEL BLID Clock Outrook                          |

| SEL_PLI_2   38                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |               |                                                      |     |                                                          |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | ĺ             | 33                                                   |     | 0 0 2.5 x DCLK                                           |

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                                                      |     | 0 1 3 x DCLK                                             |

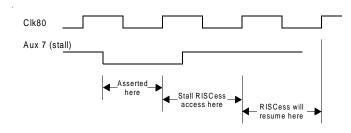

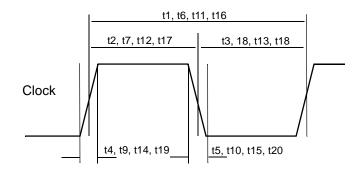

| 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |                                                      |     |                                                          |